**DECEMBER 1983**

# semiconductor

# MSM5832 MICROPROCESSOR REAL-TIME CLOCK/CALENDAR

# **GENERAL DESCRIPTION**

The MSM5832 is a monolithic, metal-gate CMOS integrated circuit that functions as a real time clock/calendar for use in bus-oriented microprocessor applications. The on-chip 32,768 Hz crystal controlled oscillator time base is counted down to provide addressable 4-bit I/O data of SECONDS, MINUTES, HOURS, DAY-OF-WEEK, DATE, MONTH, and YEAR. Data access is controlled by 4-bit address, chip select, read, write and hold inputs. Other functions include 12H/24H format selection, leap year identification and manual ±30 second correction.

The MSM5832 normally operates from a 5 volt  $\pm$  5% supply. Battery back-up operation down to 2.2 volts allows continuation of time keeping when main power is off. One test input facilitates rapid testing of the time keeping operations. The MSM5832 is offered in an 18-lead dual-in-line plastic (RS suffix) package.

#### **FEATURES**

Microprocessor bus-oriented

| • TIME   | MONTH | DATE |   | YEAR |   | DAY OF WEEK |

|----------|-------|------|---|------|---|-------------|

| 23:59:59 | 12 -  | 31   | - | 99   | - | 7           |

- 4-BIT DATA BUS

- 4-BIT ADDRESS

- · Read, Write, Hold, Chip select inputs

- Interrupt signal outputs—1024, 1, 1/60, 1/3600 Hz

- 32.768 KHz crystal controlled operation

- · Leap year register bit

- 12 or 24 hour format

- ±30 second error correction

- Single 5 volt power supply

- Back-up battery operation to VDD = 2.2 V

- Low Power Dissipation 90 μw Max. at VDD=3 V 2.5 mw Max. at VDD=5 V

- High Density 300 mil 18-Pin Package

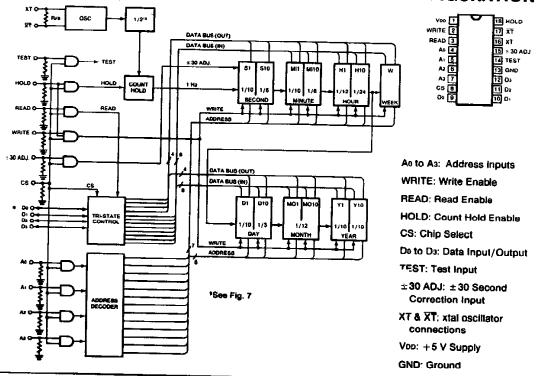

### **FUNCTIONAL BLOCK DIAGRAM**

## PIN CONFIGURATION

#### **FUNCTION TABLE**

#### FIGURE 1

| ADI | RES | SINP | UTS | INTERNAL |    | DAT | A 1/C          | •  | DATA   |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

|-----|-----|------|-----|----------|----|-----|----------------|----|--------|----------------------------------------------------------------------------------------------|--|--|-----|---|---|---|-----|--|---|--|--|--|--|-----|--|-----|--|---|-----|---------------------------------------------------|

| Ao  | A1  | A2   | Ás  | COUNTER  | Do | D1  | D <sub>2</sub> | Ds | LIMITS | NOTES                                                                                        |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 0   | 0    | 0   | S 1      | •  | +   | •              | *  |        |                                                                                              |  |  | • • | * | ٠ | * | • • |  | • |  |  |  |  | • • |  | + + |  | * | 0~9 | Si or Sio are reset to zero irrespective of input |

| 1   | 0   | 0    | 0   | S 10     | *  | ٠   | ٠              |    | 0~5    | data Do~Ds when write instruction is executed with address selection                         |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 1   | 0    | 0   | MI 1     | ٠  |     | •              | •  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 1   | 1   | 0    | 0   | MI 10    | •  | •   | ٠              |    | 0~5    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 0   | 1    | 0   | H 1      | •  |     | ٠              | ٠  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 1   | 0   | 1    | 0   | H 10     | •  | •   | t              | t  | 0~1    | D2="1" for PM D3="1" for 24 hour format D2="0" for AM D3="0" for 12 hour format              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 1   | 1    | 0   | w        | *  | *   | •              |    | 0~6    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 1   | 1   | 1    | 0   | D 1      | *  | *   | *              | *  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 0   | 0    | 1   | D 10     | ٠  | •   | t              |    | 0~3    | D <sub>2</sub> ="1" for 29 days in month 2<br>D <sub>2</sub> ="0" for 28 days in month 2 (2) |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 1   | 0   | 0    | 1   | MO 1     | *  | ٠   | •              | *  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| ٥   | 1   | 0    | 1   | MO 10    | •  |     | ~              |    | 0~1    | 1                                                                                            |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 1   | 1   | 0    | _ 1 | Y 1      | •  | •   | •              | *  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

| 0   | 0   | 1    | 1   | Y 10     | ٠  | *   | ٠              | 4  | 0~9    |                                                                                              |  |  |     |   |   |   |     |  |   |  |  |  |  |     |  |     |  |   |     |                                                   |

<sup>(1) \*</sup>data valid as "0" or "1"

blank does not exist (unrecognized during a write and held at "0" during a read)

†data bits used for AM/PM, 12/24 HOUR and leap year must be masked from the H10 and D10 registers for correct time to be read.

(2) If D2 previously set to "1", upon completion of month 2 day 29, Q2 will be internally reset to "0"

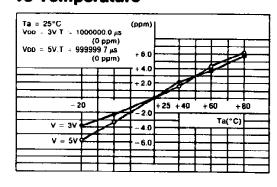

# TYPICAL CHARACTERISTICS—Oscillator Frequency Deviations **Frequency Deviation** vs Temperature

# **Frequency Deviation** vs Supply Voltage

### FIGURE 2

#### FIGURE 3

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating              | Symbol | Value           | Unit |

|---------------------|--------|-----------------|------|

| Supply Voltage      | VDD    | -0.3 ∼ 7.0      | V    |

| Input Voltage       | Vin    | -0.3 ∼ Vop +0.3 | V    |

| Data I/O Voltage    | Vo     | -0.3 ∼ Vpp +0.3 | V    |

| Storage Temperature | Talg   | -55 ∿ 150       | •c   |

Note: Stresses above those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or at any other condition above those indicated in the operational sections of this specifica-tion is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **OPERATING CONDITIONS**

| Parameter                | Symbol | Min. | Тур.   | Max.    | Unit | Conditions     |

|--------------------------|--------|------|--------|---------|------|----------------|

| Supply Voltage           | Voo    | 4.75 | 5      | 5.25    | V    | 5V ± 5%        |

| Standby Supply Voltage   | Voos   | 2.2  | 5      | 7       | V    |                |

| loout Circuit Augi       | ViH    | 3.6  | 5      | Voo     | V    | Voc = 5V ± 5%  |

| Input Signal Level       | VIL    | -0.3 | 0      | 8.0     | v    | Respect to Gnd |

| Crystal Oscillator Freq. | f(xT)  |      | 32.768 | 65.536° | KHz  |                |

| Operating Temperature    | Та     | - 30 | 1      | +85     | °C   |                |

<sup>\*</sup>Device will run at  $2\times$  speed when operating at 65.536KHz f(XT)

## **DC CHARACTERISTICS**

(VDD = 5V  $\pm$  5%; TA = -30 to +85°C, unless otherwise noted)

| Parameter                | Symbol | Min.                                                          | Тур. | Max. | Unit       | Conditions                        |

|--------------------------|--------|---------------------------------------------------------------|------|------|------------|-----------------------------------|

| Input Current            | Ітн    | 10                                                            | 25   | 50   | μА         | Vin = 5V                          |

| (1)                      | lı.    | -1                                                            |      | 1    | μА         | Vin = OV                          |

| Data I/O Leakage Current | ILD    | -1                                                            |      | 1    | μΑ         | Vi/o = 0 to Vpp, CS = "0"         |

| Output Low Voltage       | Vol    |                                                               |      | 0.4  | ٧          | lo = 1.6 ma, CS = "1", READ = "1" |

| Output Low Current       | lor    | 1.6                                                           |      |      | mΑ         | Vo = 0.4V, CS = "1", READ = "1"   |

| Output High Voltage      | Vон    | Open Drain n-MOS Output; Depends on value of Pull-up Resistor |      |      |            |                                   |

| Output High Current      | Іон    |                                                               |      |      | See Fig. 7 |                                   |

| Operating Supply Current | loos   |                                                               |      | 30   | μА         | Voo = 3V, Ta = 25°C               |

| Operating Supply Current | 100    |                                                               |      | 500  | μΑ         | Voo = 5V, Ta = 25°C               |

<sup>(1)</sup> XT,  $\overline{\text{XT}}$  and DO $\sim$  D3 excluded.

#### **AC CHARACTERISTICS**

#### **CAPACITANCE**

TA = 25°C, f = 1 MHz

| Parameter                | Symbol | Min. | Typ. | Max. | Unit |

|--------------------------|--------|------|------|------|------|

| Input/Output Capacitance | Ci/o   |      |      | 8    | ρF   |

| Input Capacitance        | Cin    |      |      | 5    | pF   |

Note: This parameter is periodically sampled and not 100% tested.

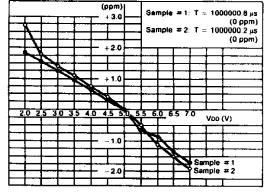

#### **READ CYCLE**

$(Voc = 5V \pm 5\%; Ta = 25°C)$

| Parameter           | Symbol      | Min. | Тур. | Max. | Unit |

|---------------------|-------------|------|------|------|------|

| HOLD Set-up Time    | tHs         | 150  |      |      | μS   |

| HOLD Hold Time      | tнн         | 0    |      |      | μS   |

| HOLD Pulse Width    | thw         |      | -    | 1    | SEC  |

| READ Hold Time      | ŧян         | 0    |      |      | μS   |

| ADDRESS Access Time | <b>t</b> RA |      |      | 6    | μS   |

| READ Access Time    | taa         |      | .3   | .6   | μS   |

Notes: 1. A Read occurs during the overlap of a high CS and a high READ 2. Output Load: 1 TTL Gate, CL = 50 pf and RL = 4.7 K $\Omega$  3. CS may be a parmanent "1", or may be coincident with HOLD pulse

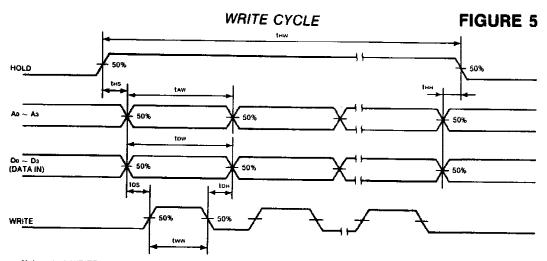

#### WRITE CYCLE

(VDD = 5V ± 5%; Ta = 25°C)

| Symbol | Min.                        | Max.                                          | Unit                                                |

|--------|-----------------------------|-----------------------------------------------|-----------------------------------------------------|

| tHS    | 150                         |                                               | μS                                                  |

| thh    | 0                           |                                               | μŞ                                                  |

| thw    |                             | 1                                             | SEC                                                 |

| taw    | 1.7                         |                                               | μS                                                  |

| tow    | 1.7                         |                                               | μS                                                  |

| tos    | 0.5                         |                                               | μS                                                  |

| tрн    | 0.2                         |                                               | μS                                                  |

| tww    | 1.0                         |                                               | μS                                                  |

|        | ths thH thW taw tow tos tDH | ths 150 thH 0 thW 1.7 tow 1.7 tos 0.5 tbH 0.2 | ths 150 thH 0 thW 1 taw 1.7 tow 1.7 tos 0.5 tbH 0.2 |

Notes: 1. A WRITE occurs during the overlap of a high CS, a high HOLD and a high WRITE 2. CS may be a permanent "1", or may be coincident with HOLD pulse

### **FUNCTIONAL DESCRIPTION**

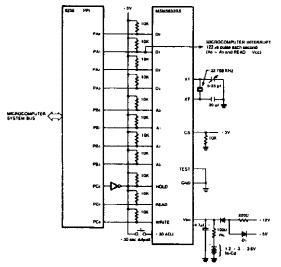

A block diagram of the MSM5832 microprocessor real-time clock/calendar and a package connection diagram are shown on the first page. Figure 9 illustrates a method of interfacing between the clock/calendar circuit and a micro processor. Figures 9, 10 and 11 illustrate alternative standby power supply circuits. A function table listing relationships between address inputs, data input/output and internal counter selection is shown in Figure 1. Unless otherwise indicated, the following descriptions are based on the block diagram.

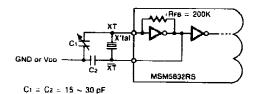

32.768 K Hz OSCILLATOR (pins 16 and 17): An internal inverting amplitter with feedback resistor, RFB, is connected with a crystal and two capacitors as shown in Figure 6 to form a stable, accurate oscillator—which serves as the precision time base of the circuit. Capacitors C1 and C2 in series provide the parallel load capacitance required for precise tuning of the quartz crystal. Typical oscillator performance as a function of ambient temperature and supply voltage is shown in Figures 2 and 3 respectively.

# OSCILLATOR CIRCUIT

#### FIGURE 6

CHIP SELECT (pin 8): Connecting CS input to VDD enables all inputs and outputs. Unconnected—pull-down to GND is provided by an internal resistor—or connecting CS to GND will disable HOLD, WRITE, READ, ±30 ADJ, Do~D3, Ao~D3 and TEST.

As shown in Figure 9 CS can be used to detect system power failure by connecting system power (+5V) to CS, so that when system power is on, all inputs and outputs will be enabled, and when system power is off, all inputs and outputs will be disabled The threshold voltage of CS is higher than all other inputs to insure correct operation of this function.

HOLD (pin 18): Switching this input to Vcc inhibits the internal 1Hz clock to the S1 counter. After the specified HOLD sat-up time (150 µs), all counters will be in a static state, thus allowing arror-free read or write operations. So long as the HOLD pulse width is less than 1 second, accuracy of the real time will be undisturbed. Pull-down to GND is provided by an internal resistor.

READ (pin 3): Read function as shown in Figure 4 is enabled when READ is switched to Vob. Pull-down to GND is provided by an internal resistor.

WRITE (pin 2): Write function as shown in Figure 5 is enabled when WRITE is switched to VDD. Pull-down to GND is provided by an internal resistor.

$\pm$  30 ADJ (Pin 15): Momentarily connecting this input to Vcc (>31.25 ms) will reset seconds (S1, S10 counters and  $2^{11}\sim 2^{13}$  frequency dividers) to 00; if seconds were 30 or more, one minute is added to the minutes (Mi 1 counter) and if seconds were less than 30, the minutes are unchanged. Pull-down to GND is provided by an internal resistor.

Ae  $\sim$  As (pins 4  $\sim$  7): Address inputs, used to select internal counters for read/write operations (see function table—Figure 1). A "1" is defined as VDD; a "0" is GND. Pull-down to GND is provided by internal resistors.

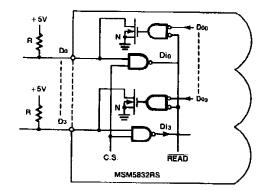

De ~ D3 (pine 9 ~ 12): Data Inputs/Outputs, two-way bus lines controlled by READ and WRITE inputs. As shown in Figure 7 external pull-up resistors of 4.7K or higher are required by the open-drain N-channel MOS outputs. D3 is the MSB, D0 is the LSB.

TEST (pin 14): Normally this input is unconnected—pull-down to GND is provided by an internal resistor—or connected to GND. With CS at VDD, pulses to VDD on the TEST input will directly clock the S1, MI10, W, D1 and Y1 counters, depending on which counter is addressed (W and D1 are selected by D1 address in this mode only). Roll-over to next counter is enabled in this mode.

Max. Input Freq = 10KHz

### DATA I/O CIRCUIT

#### FIGURE 7

#### REFERENCE SIGNAL OUTPUT

Reference signals are available as outputs on Do ~Ds if CS, READ and Ao ~ As are at VDD. Refer to Figure 8 for specifics. As shown in Figure 9 these signals may be used to generate interrupts for the microprocessor.

# REFERENCE SIGNAL OUTPUTS FIGURE 8

| CONDITIONS  | ОИТРИТ | REFERENCE<br>FREQUENCY | PULSE<br>WIDTH      |

|-------------|--------|------------------------|---------------------|

| HOLO = L    | Do (1) | 1024 Hz                | duty 50 %           |

| READ = H    | D1 (2) | 1 Hz                   | 122.1 μ5            |

| C.S. = H    | Os (2) | 1/60 Hz                | 122.1 µs            |

| A0 ~ A3 = H | D3 (3) | 1/3600 Hz              | عبر 122.1 <u>بع</u> |

- (1) 1024 Hz signal at Do not dependent on HOLD input level. Use this signal for trimming the quartz oscillator. Probe capacitance will load the oscillator if a probe is placed on XT or XT causing erroneous readings. Trim to 976.5825 µs ± .0015 µs

- (2) Negative Pulse, Negative True

- (3) Positive Pulse, Positive True

# TYPICAL APPLICATION—Use with Programmable Peripheral Interface (PPI)

#### FIGURE 9

Suggested XTAL Sources: 1.) Statek CX-IV-32.768

#### NOTE A:

This circuit combines battery charging with switching logic to power the 5832/58321 from the battery when system power fails. RL is a current limit to protect the battery if Vbb is accidentally shorted. Since Diode D1's cathode is at the system power supply (+5V), D1 and D2's anodes will be one diode drop positive from system power and the cathode of D2 will also track the system power supply. VCHG and RCHG are chosen to trickle charge the batteries. VCHG need not be a regulated voltage and the unregulated voltage into the system +5V supply is ideal. When system power falls, D1 and D2 prevent the battery from trying to power the system. Vbb will be the battery voltage whenever VCHG is less than the battery voltage.

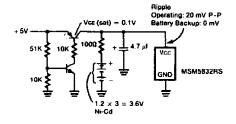

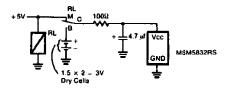

# TYPICAL APPLICATIONS—Alternative Standby Power Supply Circuits

#### FIGURE 10

#### FIGURE 11

(0.8) XAM

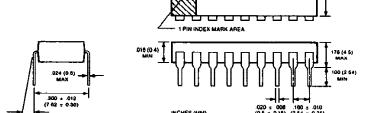

#### **PACKAGE SPECIFICATIONS**

18 LEAD PLASTIC (RS)

OKI SEMICONDUCTOR, INC. 785 NORTH MARY AVENUE, SUNNYVALE, CALIF. 94086-2909

TELEPHONE: (408) 720-1900 FAX: (408) 720-1918

OKI Semiconductor reserves the right to make changes in specifications at any time and without notice. The information furnished by OKI Semi-conductor in this publication is believed to be accurate and reliable. However, no responsibility is assumed by OKI Semiconductor for its use; nor for any infringements of patents or other rights of third parties resulting from its use. No license is granted under any patents or patent rights of OKI.

This datasheet has been download from:

www.datasheetcatalog.com

Datasheets for electronics components.